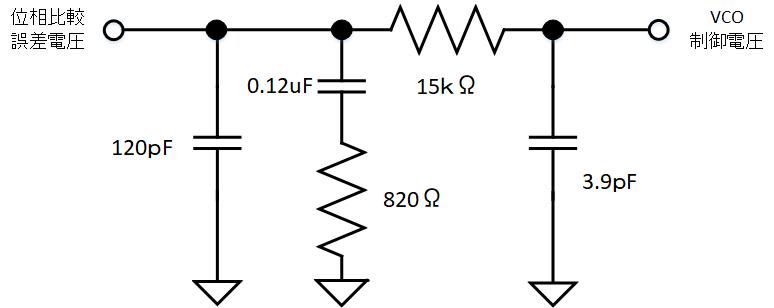

PLL方式の局部発振回路に必須のループフィルタです。

PLLICの位相比較信号(パルス)を平滑しVCOの発振周波数を制御します。

このフィルタで近接の位相雑音が低減され、またPLLのロックアップタイムが決定されます。

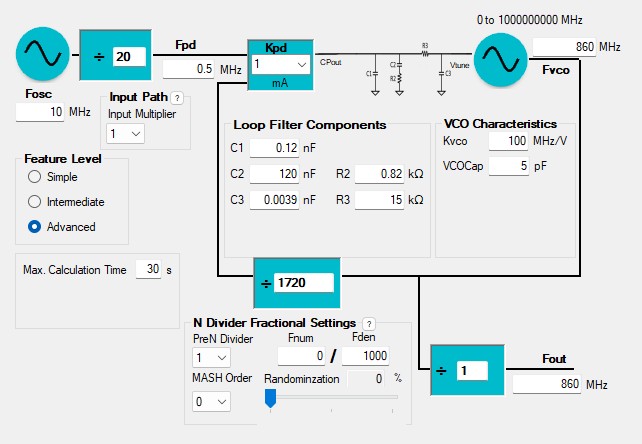

今回はTI(テキサスインスツルメンツ)が公開しているアプリケーションソフト「PLLatinum Sim」を利用しました。

基準信号周波数が10MHz、位相比較周波数を500kHzとし出力周波数を860MHzとしました。KVCO(VCO感度)を100MHz/Vとし計算させました。計算されたループフィルタは次のようになりました。

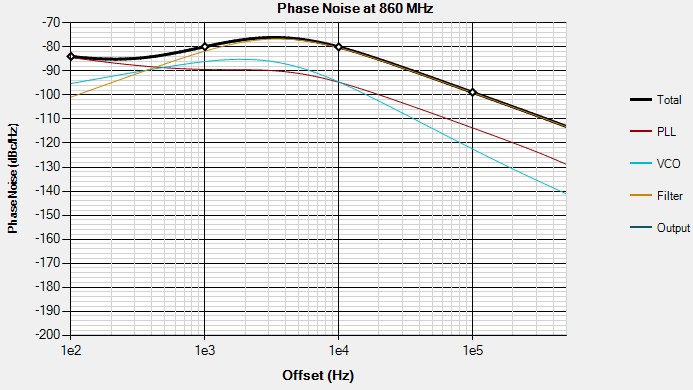

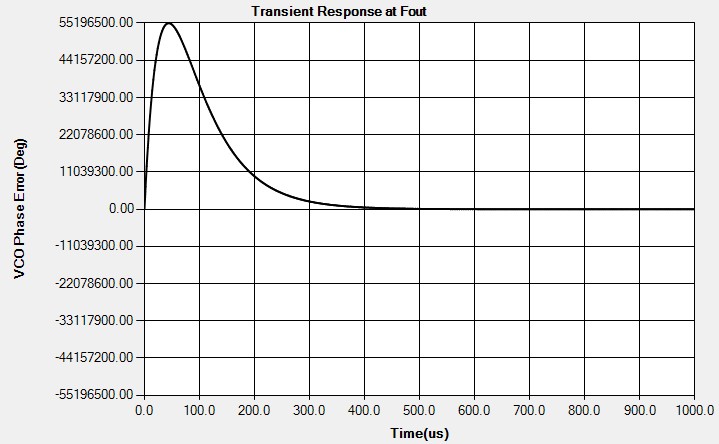

シミュレーションによる位相雑音とロックアップタイムの様子を示します。

VCOの帯域が非常に広くVCO感度が高いため、位相雑音が多めになっています。

過渡応答は500usecで落ち着いているため、0.5msでロックする予想です。

コメント